📅 Wednesday, May 22nd, 2024

Sports do not build character. They reveal it.

— Heywood Broun

ECS154A Lecture: ARM instructions

-

Read Ch. 6-7

-

Refer to this article on how mov immediate encoding works.

-

ways to set flags

cmp- append

sto instruction mnemonic (note that by default, ALU instructions do not touch the CPSR (flags) registers)

-

ARM instructions contain conditional codes, which are represented in the mnemonics as suffixes (e.g., ne). They enable conditional execution of instructions depending on the flag values, which kind of emulates branches without jumping. This is why it’s a nice thing that instructions don’t modify the CPSR by default unless

sis present; if they did then conditional execution will only work for one instruction. -

b <target>is an unconditional branch, but we can also make use of condition codes. -

instruction encoding design principles

- Try to enforce a uniform instruction format for simplicity. Compromises will be needed at times for a good design.

- Keep the number of instructions small.

-

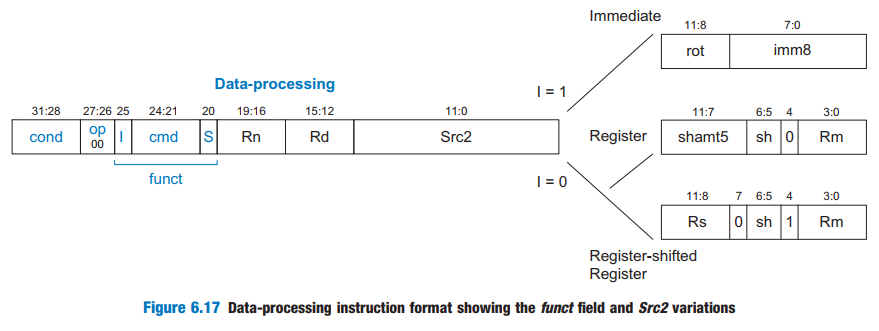

data processing instruction format (see fig below)

- Notice that it’s easy to extract the immediate (Src2) through AND.

- funct: specifies the function to use within the op

- cmd: instruction kind: e.g., add, sub, etc

- I: whether Src2 is immediate (1) or register (0)

- S: whether to set condition flags

- Src2

- Immediates are encoded via a 4-bit right rotate amount (as a multiple of 2), and a 8-bit value , so the final result is ror . For mov, large immediates have to be either pieced together with multiple instructions (e.g., a mov plus more orr’s), or be directed loaded from the memory via ldr. 32-bit constants can be achieved through rotations.

SOC001: relationships cont’d

- recall McDonaldization relates to efficiency, calculability, standardization, and control.

- Rationality (Weber) refers to an increased focus on work

- Modernity (Giddens) is defined as a shift to more complex decision-making in social life