📅 Wednesday, May 8th, 2024

Every day I remind myself that my inner and outer life are based on the labors of other men, living and dead, and that I must exert myself in order to give in the same measure as I have received and am still receiving.

— Albert Einstein

ECS154A Lecture: timing

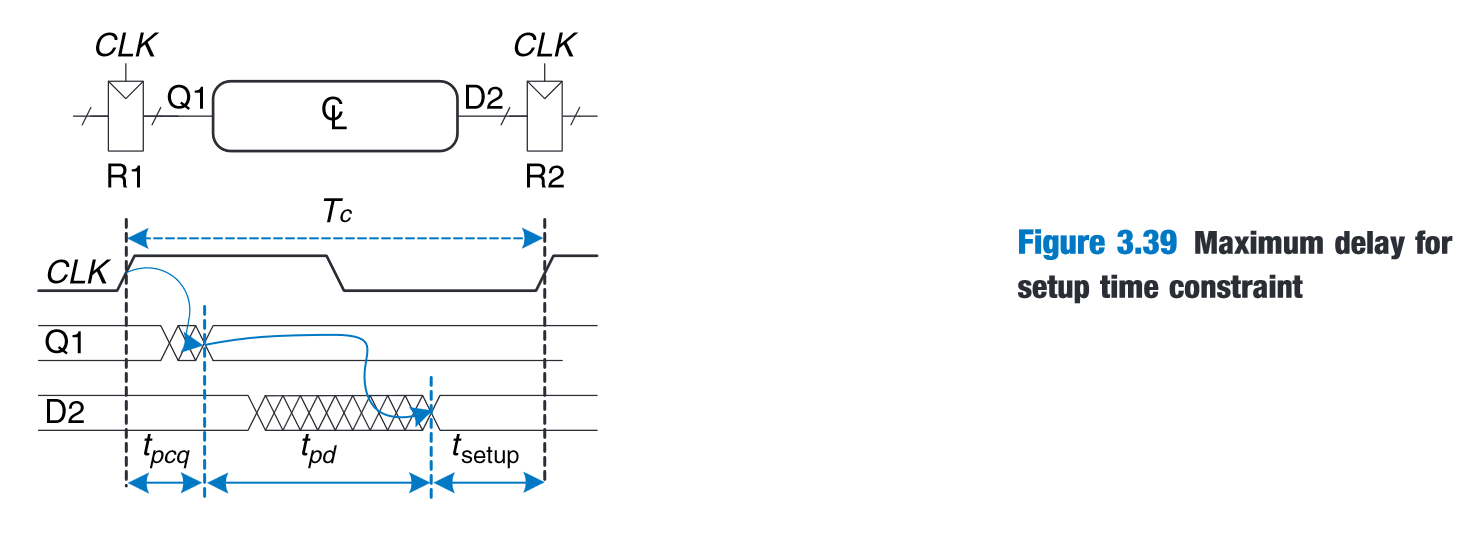

Consider a circuit in which a combinational circuit takes input from a register and outputs to a register (could be the same register).

- Assume that, for the purpose of this course, all flip flops have the same delays.

- contamination delay (min delay) : time for output to change after the input changes

- also : contamination delay of a flip-flop (i.e., from clock to output q)

- We can make use of this to maintain an aperture for positive clock edge.

- propagation delay (max delay) : time for output to settle after the input changes

- also : propagation delay of a flip-flop (i.e., from clock to output q)

- The contamination delay of a register output must be longer than the hold time for the next register’s input.

- dynamic discipline: synchronous (i.e., clocked) sequential circuit inputs must be stable during aperture time

- Don’t consider input bubbles as separate inverters when computing delays.

The setup time constrains the combinational circuit’s max delay. The setup time and flip flop timing is usually not changeable. We need to account for the delays of the flip flop and the delays of the combinational circuit. Note that the only things we can change in the equation below is the cycle time and the propagation delay

where is defined as the sequencing overhead.

Therefore, the only ways we can fix setup time violations are:

- Adjust the cycle time (doesn’t always work).

- Rework the circuit to adjust the propagation delay.

On the other side, the hold time constrains the min delay such that the latter has to be greater than the former in order for the circuit to maintain its output after the positive clock edge. Same as before, we need to consider the contamination delays of both the register and the combinational circuit. We cannot control and , so we can only adjust the contamination delay by artificially adding gates to the short path.

When doing timing analysis (e.g., checking if a circuit obeys the timing constraints or if it runs under a certain clock speed), simply plug the relevant numbers to the setup & hold time constraint equations.

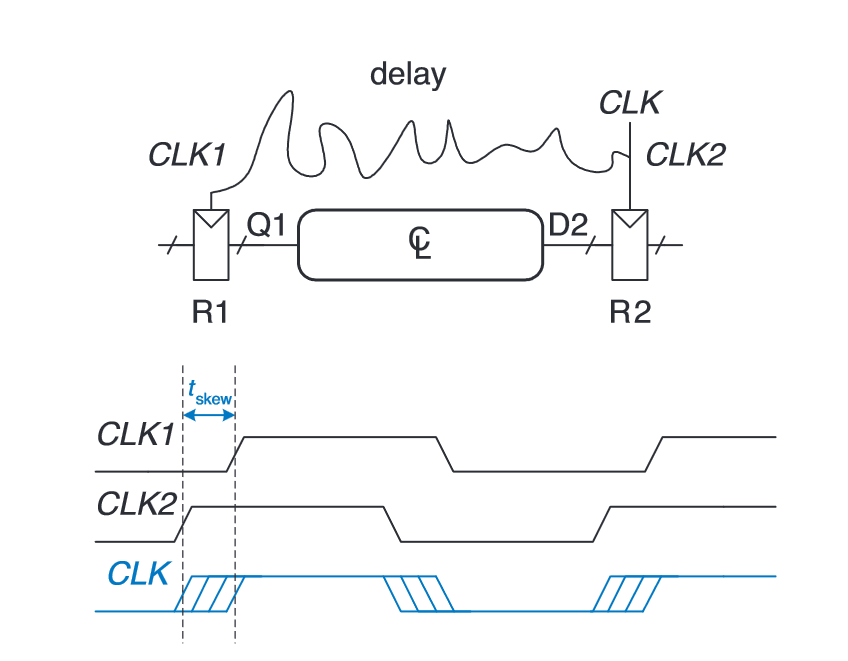

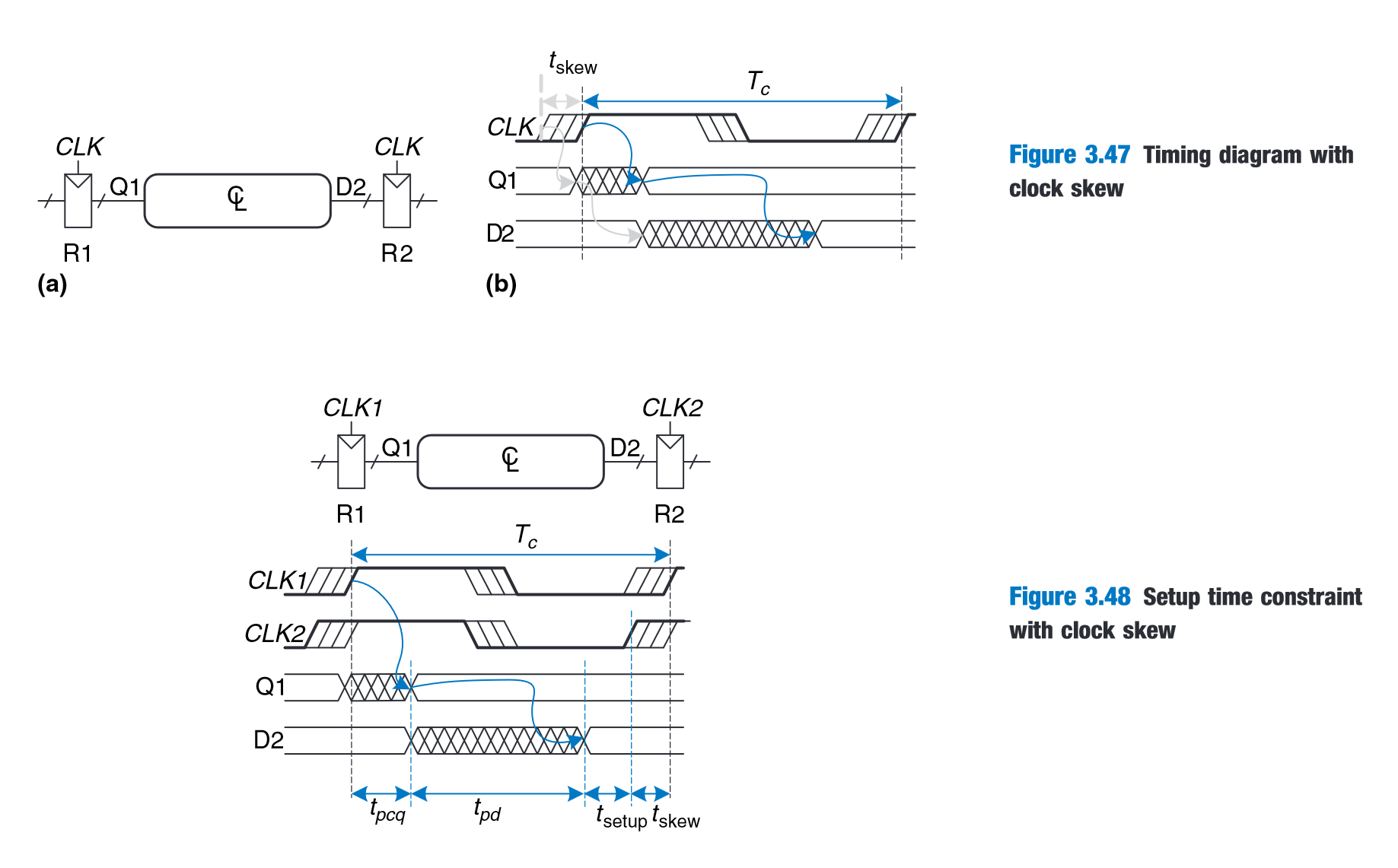

In most cases, different registers will have positive edges at slightly different times due to the lengths of wiring, etc. This phenomenon is called clock skew.

We need to account for the worst-case scenario in which the input register clock signal is very late and the output register clock signal is very early.

SOC001 Lecture: Sociological Research cont’d

- typical research methods

- survey (quantitative)

- interview (qualitative)

- participant observation (qualitative - field research)

- ethnography: study of group or culture (qualitative - field research)

- secondary data analysis: interpret data collected by another party (quantitative)

- content analysis: analyze existing audiovisual materials (books, TV shows, podcasts, social media posts, etc) (both)

- research ethics

- do no harm (physical, emotional, leaking PII, etc)

- Weber’s value neutrality

- Be clear about personal position and biases

- ASA code of ethics